Description

This report covers the Metal Chemicals market trends and supply-chain as it applied to Advanced Packaging (wafer level) and Semiconductor Device Manufacturing (damascene process). Included are forecasts for copper plating and additives, market shares, technical trends, and supplier profiles. Also included in the appendix is a supplier product comparison table of publicly available information on plating products used for advanced packaging.

Featured Press Release on Metal Chemicals Market Updates and Report Highlights:

Table of Contents:

Click here for a PDF download of table of contents

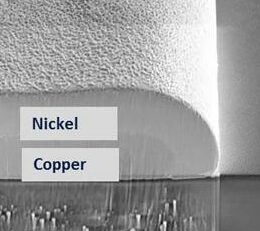

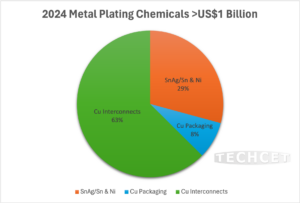

1.1 EXECUTIVE SUMMARY 9 1.1 EXECUTIVE SUMMARY 10 1.2 ADVANCED PACKAGING PER WAFER STARTS 11 1.3 DEVICE DEMAND DRIVERS - LOGIC 12 1.4 CU PLATING FORECAST FOR CU INTERCONNECTS AND ADVANCED PACKAGING 13 1.5 MARKET SHARES 14 1.6 SUPPLIER ACTIVITIES – VARIOUS ANNOUNCEMENTS 15 1.7 RISK FACTORS 16 1.8 ANALYST ASSESSMENT 17 2 SCOPE, PURPOSE AND METHODOLOGY 18 2.1 SCOPE 19 2.2 PURPOSE 20 2.3 METHODOLOGY 21 2.4 OVERVIEW OF OTHER TECHCET CMR™ REPORTS 22 3 SEMICONDUCTOR INDUSTRY MARKET OUTLOOK 23 3.1 WORLDWIDE ECONOMY 24 3.1.1 SEMICONDUCTOR INDUSTRIES TIES TO THE GLOBAL ECONOMY 26 3.1.2 SEMICONDUCTOR SALES GROWTH 27 3.1.3 TAIWAN OUTSOURCE MANUFACTURER MONTHLY SALES TRENDS 28 3.2 CHIPS SALES BY ELECTRONIC GOODS SEGMENT 29 3.2.1 SMARTPHONES 30 3.2.2 PC UNIT SHIPMENTS 31 3.2.3 SERVERS / IT MARKET 34 3.3 SEMICONDUCTOR FABRICATION GROWTH & EXPANSION 35 3.3.1 FAB EXPANSION ANNOUNCEMENT SUMMARY 36 3.3.2 WW FAB EXPANSION DRIVING GROWTH 38 3.3.3 EQUIPMENT SPENDING TRENDS 39 3.3.4 TECHNOLOGY ROADMAPS 40 3.3.5 FAB INVESTMENT ASSESSMENT 41 3.4 POLICY & TRADE TRENDS AND IMPACT 42 3.5 SEMICONDUCTOR MATERIALS OUTLOOK 43 3.5.1 COULD MATERIALS CAPACITY LIMIT CHIP PRODUCTION SCHEDULES? 44 3.5.2 LOGISTICS ISSUES EASED DOWN 45 3.5.3 TECHCET WAFER STARTS FORECAST THROUGH 2027 46 3.5.4 TECHCET’S MATERIAL FORECAST 47 4 METAL CHEMICALS MARKET BY SEGMENT 48 4.1 DEFINITIONS 49 4.1.1 DEFINITIONS, CONTINUED 50 4.2 METAL PLATING CHEMICALS MARKET OVERVIEW 51 4.2.1 OVERVIEW – CU ADVANCED PACKAGING AND CHIP INTERCONNECTS METALLIZATION 52 4.2.2 OVERVIEW - PLATING MARKET TRANSITIONAL TRENDS 53 4.3 ADVANCED PACKAGING METALLIZATION – MARKET DRIVERS 54 4.3.1 ADVANCED PACKAGING - ADDITIVES FOR CU PLATING REVENUE 55 4.3.2 ADVANCED PACKAGING – COPPER CHEMICALS REVENUE 56 4.3.3 ADVANCED PACKAGING ADDITIVE VOLUMES 57 4.3.4 OTHER PLATING MATERIALS FOR ADVANCED PACKAGING 58 4.3.5 SN / SNAG PLATING 59 4.4 CHIP INTERCONNECTS GROWTH TRENDS 61 4.4.1 CHIP INTERCONNECTS GROWTH DRIVERS 62 4.4.2 CHIP INTERCONNECTS CU PLATING REVENUES 63 4.4.3 CHIP INTERCONNECTS ADDITIVE VOLUMES 64 4.5 MINE LOCATIONS FOR METALS IN PLATING CHEMICALS 64 4.6 POSSIBLE CHOKE POINTS FOR METALS USED IN IC PLATING 66 4.7 FUTURE POSSIBLE DEMAND PRICE PRESSURES 67 5 TECHNICAL TRENDS 68 5.1 CHEMISTRIES USE FOR SEMICONDUCTOR METAL PLATING 69 5.2 PACKAGING TECH TRENDS 70 5.2.1 PACKAGING TECHNICAL CHALLENGES 71 5.3 TECH TRENDS 72 5.3.1 MARKET DRIVES TECHNOLOGY TRENDS 73 5.3.2 ADV LOGIC INTERCONNECT WIRING TECHNOLOGY EVOLUTION 74 5.3.3 CU INTERCONNECTS QUALIFICATION REQUIREMENTS 76 5.3.4 LOGIC METALLIZATION ROADMAP 77 5.3.5 ADV LOGIC BURIED POWER RAIL 79 5.3.6 TECHNOLOGY ROADMAP: DRAM WITH MO OR RU 80 5.3.7 PRECURSOR TECHNOLOGY ROADMAP: 3D NAND USING MO OR RU 82 5.3.8 EXAMPLE OF LOGIC PRO CESS FLOW 20 NM TO 32 NM LOGIC PVD 84 5.3.9 TECHNICAL REQUIREMENTS SUMMARY 1/2 85 6 COMPETITIVE LANDSCAPE 87 6.1 TOTAL ADVANCED PACKAGING AND INTERCONNECTS MARKET SHARES 88 6.2 OEM MARKET SHARE – PLATING EQUIPMENT 89 6.3 MARKET SHARE BY APPLICATION – CU PLATING FOR ADVANCED PACKAGING 90 6.4 REGIONAL PLAYERS AND OTHERS 91 6.5 M&A ACTIVITY 92 7 ANALYST ASSESSMENT 93 7.1 ADVANCED METAL PLATING APPLICATIONS MARKET ASSESSMENT 94 8 SUPPLIER PROFILES 95 ATOTECH BASF DUPONT INCHEON CHEMICAL COMPANY ISHIHARA CHEMICAL/UNICON ...AND MORE 9 APPENDIX A: PACKAGING TECH TRENDS 158 9.1 TECHNOLOGY CHALLENGE 159 9.1.1 METAL CLEANINGS CHALLENGE 160 9.1.2 MARKET DYNAMIC 161 9.1.3 IDM – WAFER LEVEL PLATING 162 9.1.4 MARKET DRIVERS OF ADVANCED PACKAGING APPLICATIONS 163 9.1.5 TECH TRENDS – RDL 164 9.1.6 INTERPOSERS (NOT WLPS) 166 9.1.7 TSV FILLING 2.5-3D 168 9.1.8 PACKAGING ELECTROPLATING REQUIREMENTS 169 List of Figures FIGURE 1: PLATING MATERIALS FOR ADVANCED PACKAGING AND INTERCONNECT REVENUES ($M’S) 10 FIGURE 2: WAFERS/YR & % OF PACKAGING THAT IS ADVANCED PACKAGING (AP) 11 FIGURE 3: WAFER STARTS FORECAST - ADV. LOGIC DEVICE 12 FIGURE 4: COPPER PLATING CHEMICALS REVENUES ($M’S) FOR ADVANCED PACKAGING & DEVICE CU INTERCONNECTS 13 FIGURE 5: TOTAL PLATING MARKET SHARES FOR ADVANCED PACKAGING AND SEMICONDUCTOR DEVICE MFG. 2022 14 FIGURE 6: GLOBAL ECONOMY AND THE ELECTRONICS SUPPLY CHAIN (2022) 26 FIGURE 7: WORLDWIDE SEMICONDUCTOR SALES 27 FIGURE 8: SEMICONDUCTOR INDUSTRY TREND INDICATOR – TOP TAIWAN COMPANY REVENUES 28 FIGURE 9: 2022 SEMICONDUCTOR CHIP APPLICATIONS 29 FIGURE 10: MOBILE PHONE SHIPMENTS WW ESTIMATES 30 FIGURE 11: WORLDWIDE PC AND TABLET FORECAST 31 FIGURE 12: ELECTRIFICATION TREND BY WORLD REGION 32 FIGURE 13: SEMICONDUCTOR AUTOMOTIVE PRODUCTION 33 FIGURE 14: TSMC PHOENIX INVESTMENT ESTIMATED WILL BE US US$40 B 35 FIGURE 15: CHIP EXPANSIONS 2022-2027 US$500 B 36 FIGURE 16: SEMICONDUCTOR CHIP MANUFACTURING REGIONS OF THE WORLD 38 FIGURE 17: REVENUE FORECAST - GLOBAL TOTAL EQUIPMENT SPENDING BY SEGMENT (USUS$ B) 39 FIGURE 18: OVERVIEW OF ADVANCED LOGIC DEVICE TECHNOLOGY ROADMAP 40 FIGURE 19: INTEL OHIO PLANT SITE FEB. 2023 AND ARTIST RENDERING (ON BOTTOM) 41 FIGURE 20: EUROPE CHIP EXPANSION UPSIDE 44 FIGURE 21: PORT OF LA 45 FIGURE 22: TECHCET WAFER START FORECAST BY NODE SEGMENTS** 46 FIGURE 23: GLOBAL SEMICONDUCTOR MATERIALS OUTLOOK 47 FIGURE 24: PACKAGING METALLIZATION APPLICATIONS 49 FIGURE 25: USE OF SILICON INTERPOSER 50 FIGURE 26: VERSIONS OF TSV & PROCESS FLOW EXAMPLE 50 FIGURE 27: PLATING MATERIALS FOR ADVANCED PACKAGING AND DEVICE CU INTERCONNECT REVENUES ($M’S) 51 FIGURE 28: 5-YEAR REVENUE FORECAST – CU PLATING CHEMICALS 52 FIGURE 29: WAFERS/YR & % OF PACKAGING THAT IS ADVANCED PACKAGING 54 FIGURE 30: REVENUE FORECAST – CU PLATING ADVANCED PACKAGING 55 FIGURE 31: REVENUE FORECAST - CU PILLAR & CU RDL SEGMENTED 56 FIGURE 32: ADV. PACKAGING CU CUSO4 AMOUNT DEMAND FORECAST 57 FIGURE 33: ADV. PACKAGING CU/VMS VOLUME DEMAND FORECAST ADV. PACKAGING CU PLATING ADDITIVES 57 FIGURE 34: MATERIALS STACK USING CU PILLAR (< 40 UM PITCH) 58 FIGURE 35: SN AND SNAG PLATING REVENUE 59 FIGURE 36: REVENUE FORECAST - NICKEL PLATING REVENUE 60 FIGURE 37: WAFER START FORECAST - ADV LOGIC DEVICE GROWTH FORECAST 61 FIGURE 38: METAL PLATING WAFER PASSES FORECAST 62 FIGURE 39: WW COPPER INTERCONNECT PLATING REVENUE FORECAST ESTIMATES 63 FIGURE 40: INTERCONNECT CU PLATING CHEMICAL AMOUNT DEMAND FORECAST 64 FIGURE 41: INTERCONNECT CU PLATING ADDITIVES CHEMICAL VOLUME DEMAND FORECAST 64 FIGURE 42: KEY TRENDS IN ADVANCED PACKAGING 70 FIGURE 43: CHALLENGES OF ELECTROPLATING VIA FILL 71 FIGURE 44: METAL INTERCONNECTS BY LOGIC NODE 73 FIGURE 45: INTERCONNECT METAL COMPARISON BY RESISTIVITY 74 FIGURE 46: CU CHIP INTERCONNECTS QUALIFICATION 76 FIGURE 47: LEADING EDGE LOGIC POWER RAIL SCHEMES 79 FIGURE 48: DRAM STRUCTURE 80 FIGURE 49: 3D NAND STRUCTURE 82 FIGURE 50: TOTAL PLATING FOR ADV. PACKAGING AND CU INTERCONNECT DEVICE MANUFACTURING 2022 88 FIGURE 51: PLATING EQUIPMENT OEM MARKET SHARES % 2022 89 FIGURE 52: PLATING CHEMICAL SUPPLIER FOR INTERCONNECTS AND ADVANCED PACKAGING APPLICATIONS 90 FIGURE 53: CLEANING COMPLEXITY CANNIBALIZATION TREND 97 FIGURE 54: OSATS PACKAGING BUSINESS 99 FIGURE 55: WAFER LEVEL PLATING 100 FIGURE 56: ADVANCED PACKAGING MARKET DRIVERS AND APPLICATIONS 101 FIGURE 57: COMPARISON WITH DAMASCENE- TYPE RDL 103 FIGURE 58: USE OF SILICON INTERPOSER 104 FIGURE 59: APPLE EXAMPLE INTERPOSERS 105 FIGURE 60: TSV PROCESS FLOW EXAMPLE 106 List of Tables TABLE 1: GLOBAL GDP AND SEMICONDUCTOR REVENUES* 24 TABLE 2: IMF ECONOMIC OUTLOOK* 25 TABLE 3: DATA CENTER SYSTEMS AND COMMUNICATION SERVICES MARKET SPENDING 2022 34 TABLE 4: IRDS 2022 MORE MOORE INTERCONNECT ROADMAP (2023 NOT YET RELEASED) 75 TABLE 5: LOGIC DEVICE ROADMAP FOR METALS 77 TABLE 6: METALS REQUIRED FOR DEVICE FEATURES 78 TABLE 7: DRAM USE OF MO OR RU PRESENT & FUTURE 80 TABLE 8: GENERAL PROCESS FLOW ADVANCED DRAM 81 TABLE 9: 3D NAND MATERIAL CHANGES PRESENT & FUTURE 82 TABLE 10: NUMBER OF STACKS (S) & LAYERS (L) PER GENERATION OF 3DNAND – SOME ARE ESTIMATES FOR THE FUTURE 83 TABLE 11: EXAMPLE OF LOGIC PROCESS FLOW 20 NM TO 32 NM LOGIC PVD 84 TABLE 12: TECHNICAL REQUIREMENTS SUMMARY 85 TABLE 13: TECHNICAL REQUIREMENTS SUMMARY 86 TABLE 14: REGIONAL PLAYERS – MARKET LEADER AND “OTHERS” 91 TABLE 15: CU PACKAGING APPLICATIONS AND REQUIREMENTS 108